Introduction

A clock or converter IC cannot achieve superior performance with a dirty power supply. The performance of said systems is reliant on a clean power supply.

This article examines the basic LDO topology and identifies significant sources of noise.

A key parameter of interest is the noise output which is referred to as the RMS noise measurement or the spectral noise density.

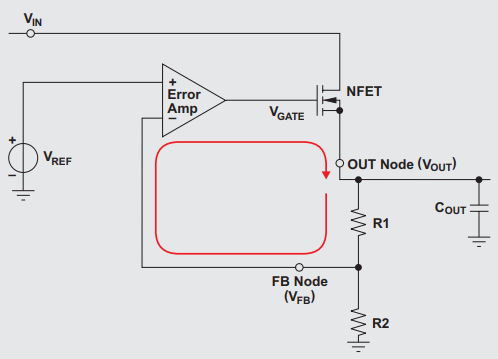

Basic LDO Topology

Negative feedback is used then compared to an internal reference to provide a constant voltage.

Three elements:

- Voltage reference

- Error amplifier

- Pass FET

V_OUT is divided by the voltage divider to supply V_FB. This is compared against V_REF. The error signal drives the FET to regulate V_OUT. 👍

V_{OUT} = \left(1 + \frac{R_1}{R_2}\right) V_{REF}

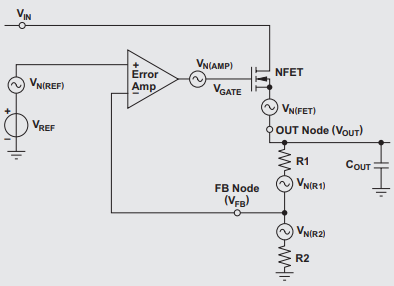

Let’s consider that the voltage reference is not ideal and contains a noise source. Let’s call it V_N(REF). Then the revised circuit looks like this:

This leads to a modification for the above formula

V_{OUT} + V_{N(OUT)} = \left( 1 + \frac{R_1}{R_2} \right) \left( V_{REF} + V_{N(REF)} \right)

V_{N(OUT)} = \left( 1 + \frac{R_1}{R_2} \right) V_{N(REF)}

According to the equation, a higher V_OUT generates more noise. The noise is then amplified via the feedback loop. Additionally, many LDO’s characterize the noise performance as a function of output voltage e.g. V_N = 18uV_rms * VOUT

Examining noise sources

In the above formula, the amplified reference noise, VN(REF) is a dominant source of noise

Looking at figure 1 above, any component that has current flowing through it can be considered a noise source. The noise equation expands to the following:

V_{N(OUT)} = V_{N(AMP)} + V_{N(FET)} + \left( 1 + \frac{R_1}{R_2} \right) \left( V_{N(REF)} + V_{N(R1)} + V_{N(R2)} \right)

Typically, the VN(REF) dominates the other noise sources. Thus the above equation simplifies to:

V_{N(OUT)} = V_{N(AMP)} + V_{N(FET)} + \left( 1 + \frac{R_1}{R_2} \right) V_{N(REF)}

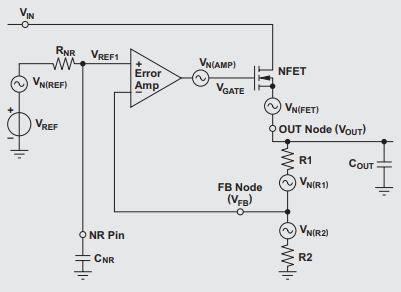

For higher performance LDOs, VN_Ref is shunted to ground via a noise-reduction (NR) pin. This is an RC filter. See the figure below

Controlling Noise

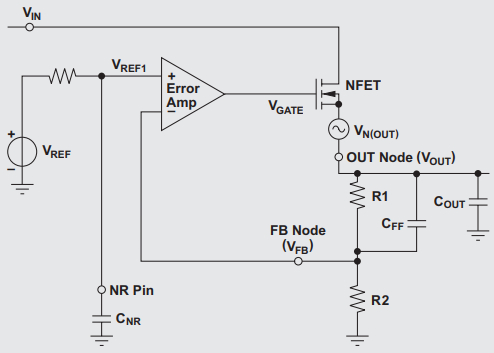

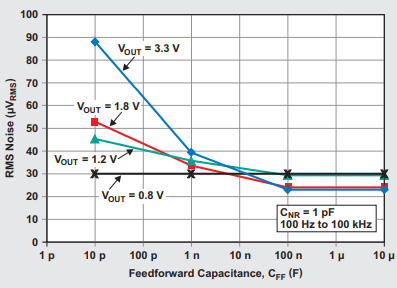

A feedforward capacitor, CFF forwards (or bypasses) output noise around R1. See Figure 4 below:

This bypassing PREVENTS the reference noise from being increased by the amplifier at frequencies higher than the resonant frequency of R1 and CFF.

Recall the formula:

f_r = \frac{1}{2 \pi R_1 C_{FF}}

The figure below demonstrates the benefits of this feedforward capacitor. A C_FF of 10uF is recommended.

In Closing

This article provided an in-depth look a LDO noise. Each block in the LDO topology was examined. The reference voltage is the dominant source of LDO noise. Techniques to mitigate noise sources were communicated.