Introduction

Upon power-up, many linear regulators experience a significant inrush current as the output capacitors charges to the input voltage.

I_{inrush} = \frac{C_{OUT} \times V_{OUT}}{t_{RISE}}

With no soft-start circuitry, I_inrush is clamped to the regulator’s current limit which is typically higher than the regulator’s rated current. This is hazardous.

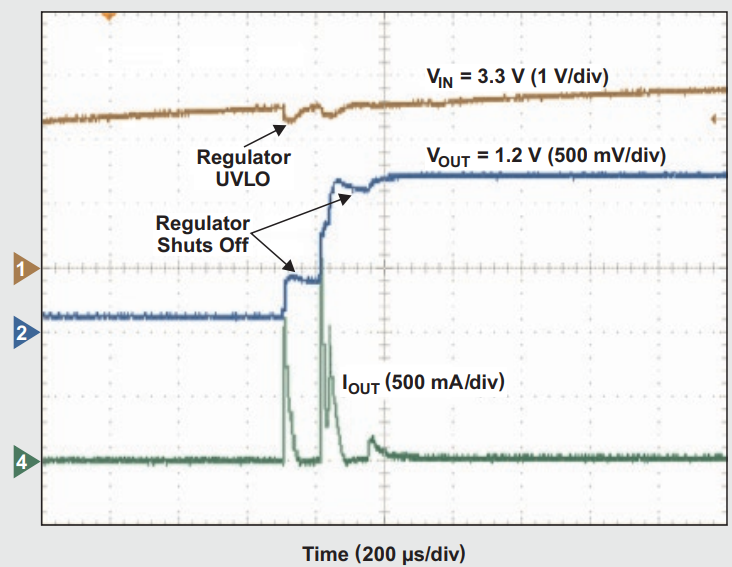

If the input power supply is current limited or connected by long inductive traces, the voltage at the regulator’s input can droop even dropping below the regulator’s undervoltage lockout (UVLO). Figure 1 demonstrates this. The regulator is struggling on its way upto regulation, shutting down temporarily while the input capacitor recharges then starts up. In Figure 1 below, the regulator shuts off when IOUT reaches its first peak.

The Solution

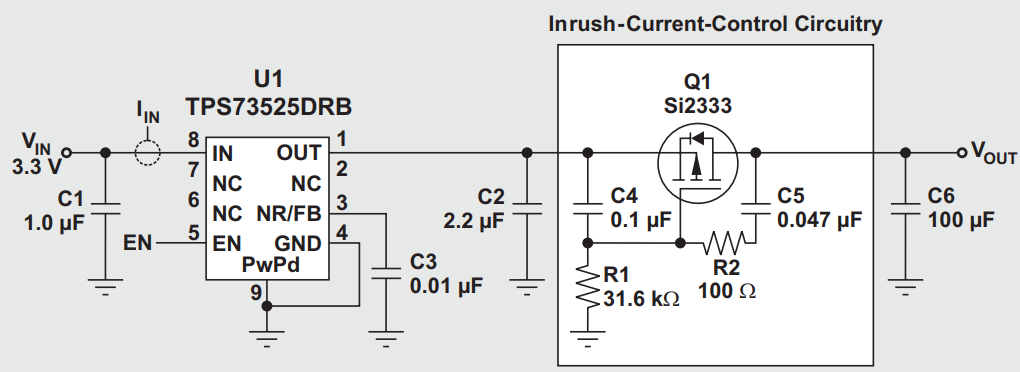

To resolve this issue, additional circuity can be implemented – i.e. a soft-start. This involves a FET (Q1), two caps (C4, C5) and two resistors (R1, R2). See Figure 2:

The inrush current is significantly reduced as the regulator sees 2.2uF (C2) rather than 100uF (C6).

Some regulators have built-in inrush current control typically via the SS pin**.** It has an internal charge pump that drives the gate of the n-channel pass element. At start-up, several hundred microseconds is required to charge the internal servo capacitor which charges the n-FET’s gate capacitance.

Newer regulators integrate soft-start circuitry. The simplest and most common integrated soft-start method ****is described below.

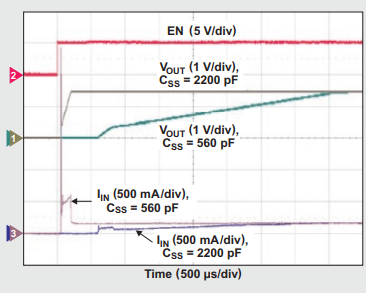

Firstly, the error amplifier’s internal reference voltage is slowly increased following an enable signal. The IC uses an external capacitor (CSS) on the soft-start pin and an internal constant-current source (ISS) to linearly charge this capacitor, which is initially tied to the regulator’s error amplifier. Once the capacitor is charged to the same value as the internal reference voltage, VREF, the IC switches the error-amplifier connection to the internal reference.

The soft-start time can be calculated as:

t_{SS} = \frac{V_{REF} \times C_{SS}}{I_{SS}}

This is beneficial to meet specific power sequencing requirements say for FPGA’s.

Figure 3 below show’s two voltage ramps for two different capacitances

In Conclusion

External soft-start circuitry is becoming obsolete due to a new generation of regulators with integrated soft start/current control.