Introduction

Choosing the right DC-DC converter involves making numerous trade-offs such as efficiency, cost and size. With the advent of newer, more efficient synchronous converters, this has thrown a spanner in this decision. This article will reveal that they are not always more efficient than their non-synchronous counterparts

Basic Operation

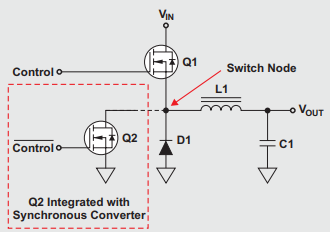

A typical diagram for a stepdown converter is shown in Figure 1 below.

It is composed of a high-side switching FET Q1, the magnetics L1, and the output capacitor C1. For a nonsynchronous buck, D1 acts as a freewheeling diode. In a synchronous buck, D1 is replaced with an internal FET Q2, eliminating the drop (and thus losses) of D1.

This is the main advantage the voltage drop across the internet FET is lower than the voltage drop across the diode. However, complexity increases to avoid a condition where both Q1 and Q2 conduct, shorting the supply.

Selecting the freewheeling diode

Four vital specifications to keep in mind:

- Reverse voltage

- Forward voltage drop

- Forward current

- Power dissipation

The reverse voltage must be 2V higher than the voltage at the high-side FET Q1. The forward drop should be as small as possible for the best efficiency. The peak-current rating must be greater than the maximum output current plus one-half the peak-to-peak inductor current.

For a low duty cycle, (i.e. at low output voltages) D1 conducts more current than the high-side FET Q1. This results in reduced efficiency

Let’s begin a discussion on efficiency

To begin a discussion on efficiency, the power dissipation needs to be considered. The main sources of power dissipation in continuous conduction mode (CCM) are the high and low-side switching losses of the FET’s and the quiescent current of the IC.

P_{Conduction\_HS} = I_{OUT}^2 \times R_{DS(on)} \times \frac{V_{OUT}}{V_{IN}}P_{SW} = V_{IN} \times V_{OUT} \times 0.5 \left( t_{Rise} + t_{Fall} \right) \times f_{SW}P_{Quiescent} = V_{IN} \times I_q

P_{Conduction\_LS} = \left[ I_{OUT}^2 \times R_{DS(on)} \times \left( 1 - \frac{V_{OUT}}{V_{IN}} \right) \right]

+ \left( 2 \times t_{Delay} \times f_{SW} \times I_{OUT} \times V_{Fwd} \right)P_{D1} = V_{D1\_Fwd} \times I_{OUT} \times \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)

According to the formula’s above, the relevant specifications relevant to efficiency are the drain-to-source resistance, drain-to-source forward voltage, duty cycle, frequency, and power MOSFET rise and fall times.

Typically, only the drain-to-source resistance, forward drop and switching frequency can be selected.

NOTE: The faster the FET rise/fall times, the less power is dissipated

Efficiency at high loads

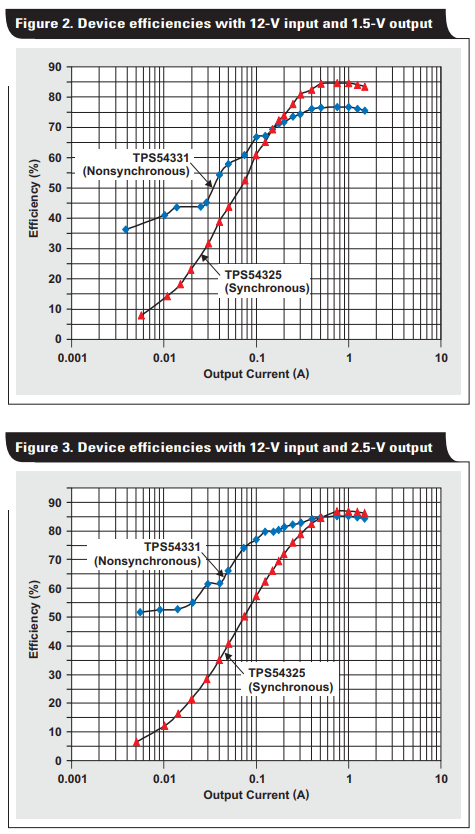

See Figures 2 and 3 below for testing performed at 12V input @1.5V and 2.5V output.

The synchronous converter has superior efficiency at higher loads. What is fascinating is that at a 2.5V output, the nonsynchronous converter had a noticeable increase in efficiency. This is due to the increased duty cycle (from 12.5% to 21%) which causes the freewheeling diode to conduct less often, thereby delivering more power to the load. Therefore, at high loads, the nonsynchronous solution is AS EFFICIENT as it’s synchronous-counterpart.

Efficiency at low loads

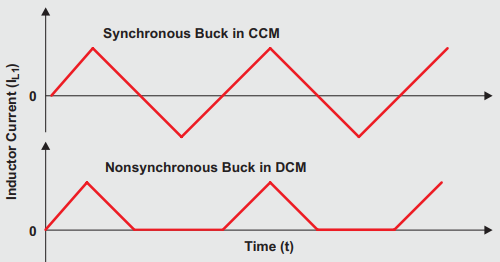

At low-loads, the nonsynchronous converter operates in discontinuous conduction mode (DCM). This means that the full inductor current is delivered to the load before the next cycle begins. Also, since the inductor current never dips below zero, it travels only in one direction. See Figure 3 below.

This explains the poor efficiency of nonsynchronous converters at light loads

With the synchronous buck converter, current is allowed to flow in both directions, and power is dissipated when reverse current flows.

In Closing

Synchronous converters have become increasingly desirable thanks to their ability to reduce the bill of materials, shrink overall size, and deliver higher efficiency. However, the efficiency varies significantly and low and heavy loading. By understanding this phenomenon, the designer can make a more informed decision.