Introduction

I2C is one of the most popular communication protocols because of its SIMPLICITY. Only two wires are required. HOWEVER, problems can arise such as:

- Slow rise times

- Crosstalk

- Higher-than-intended V_OL

- Unintended contention

- Large undershoots

This article will discuss these issues and propose solutions to remedy them

Slow rise times

This issue occurs when the signal doesn’t reaches V_IH on time. In a worst-case, this can violate the maximum rise time as dictated by the I2C protocol (Version 2.6). For reference, the maximum rise time is 1000ns for standard mode and 300ns for fast mode.

The remedy is a stronger pullup resistor. This actually means using a lower resistance value.

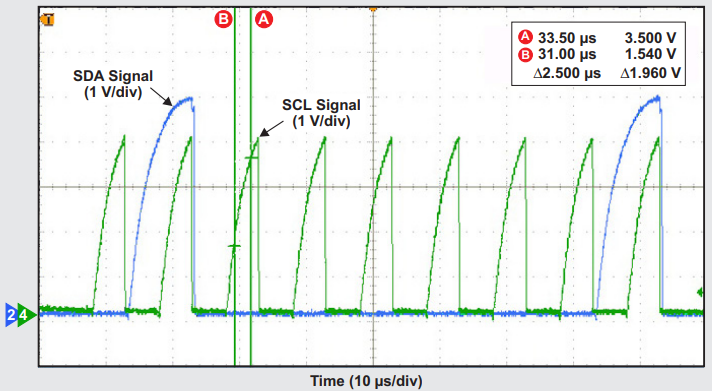

The following figure shows an SCL signal that fails to reach 70% of VCC, let alone 100% VCC. The rise time to 3.5V is 2500ns. This violates the I2C specification which states a maximum rise time of 1000ns.

Also, some I2C devices are edge-rate triggered and require a fast-enough slew rate to detect a rising pulse. A slow rise time influences the detection of said rising pulse.

Crosstalk

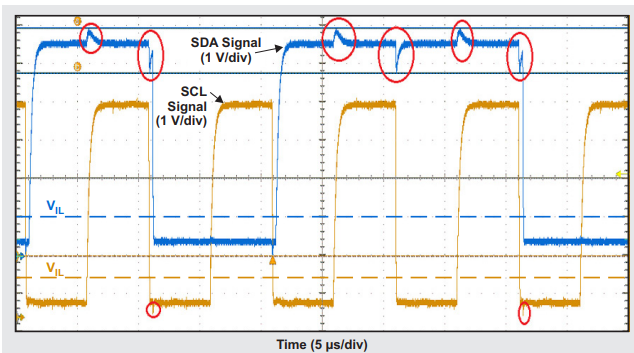

Crosstalk occurs due to fast rise/fall times of the SDA or SCL bus coupling onto the parasitic capacitance between the SDA and SCL trace.

Adding bus capacitance can help but there is a maximum according to the I2C standard, 400pF for standard and fast mode.

The BEST REMEDY is adding small series resistors on the SDA/SCL lines and to reduce parasitic capacitance between SDA and SCL traces and observing sufficient spacing between the traces.

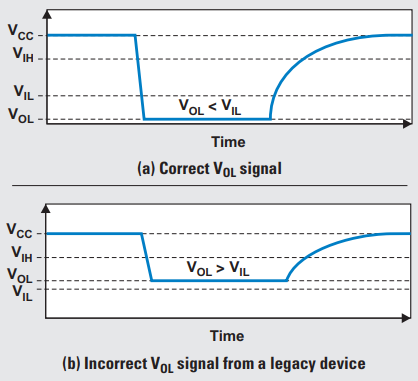

Higher than intended V_OL

This can occur due to weak FETs on older I2C devices that have difficultly pulling down the buss OR pullup resistors that are too strong (i.e. resistance values that are small).

In Figure 3a, V_OL pulls BELOW V_IL, allowing it to be interpreted as a digital LOW. The same scenario is not present in Figure 3b, where V_OL is higher than intended. This causes an unknown state which is NOT PERMISSIBLE in I2C.

Implementing a weaker pullup can resolve it however if you want the rise time to remain the same, the easier solution is implementing a BUFFER

Unintended Contention

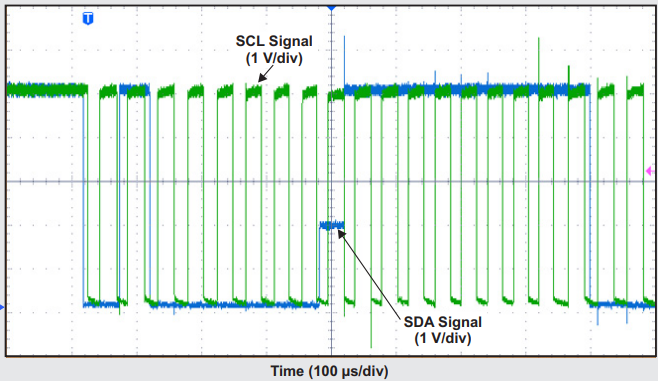

Usually I2C devices operate with an open-drain architecture. However, there are instances where a push-pull architecture is used.

In such instances, when the P-channel FET (PFET) and N-channel FET (NFET) conduct simultaneously, bus contention occurs as one device is pulling the line high while the other is pulling it low. This results in a very high V_OL which is interpreted as an unknown state.

The high I_OL can damage the FET as their not designed to since/source alot of current. The FET can only sink 0.3mA.

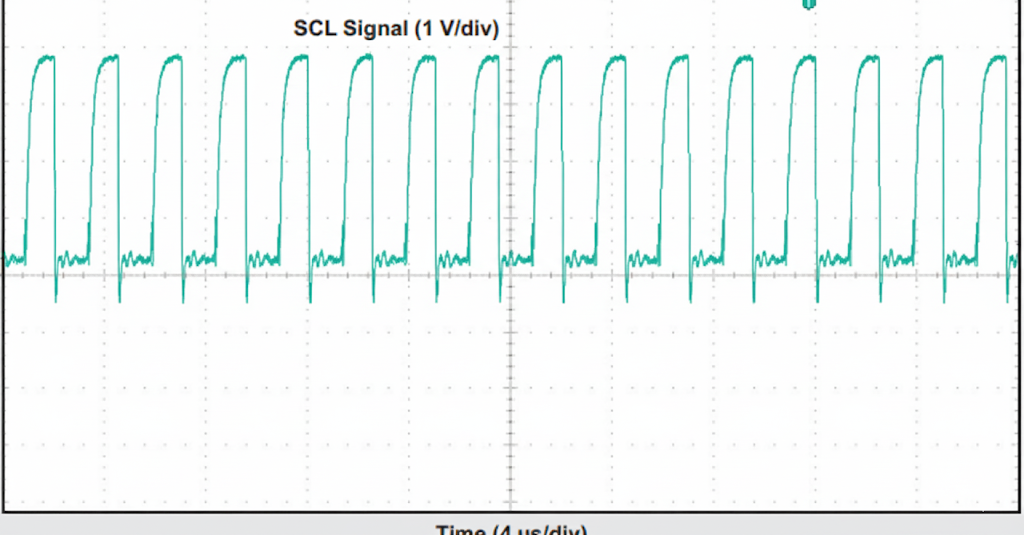

Bus contention is easy to spot as it appears as square waves. See Figure 4 below:

Undershoots

This occurs due to a large amount of parasitic inductance in addition to fast rise/fall times.

This can cause device failure as it violates the absolute maximum voltage permitted on the pin. In Figure 5, the signal reaches -0.5V. Some devices have a maximum voltage of -0.3V

If the fall time cannot be slowed down with a small series resistor and it is not possible to reduce the parasitic inductance, use a clamping diode.

Conclusion

This article has examined various issues that can occur when using the I2C protocol and recommended solutions to remedy them. It is significant to recognize and troubleshoot these issues before they result in large costs.