Introduction

This page will cover different circuits that can be used to implement a latch.

A latch is a device that can toggle between two states. A basic SPST switch can be a latch.

Latches can be permanent or momentary. i.e. if you press a button to illuminate an LED, it will continue to illuminate long after button press.

Latches comprise the most basic unit of memory.

Latches can also be called flip-flops. The two are used interchangeably. In that case JK, SR latch and D flip flops are all types of latches

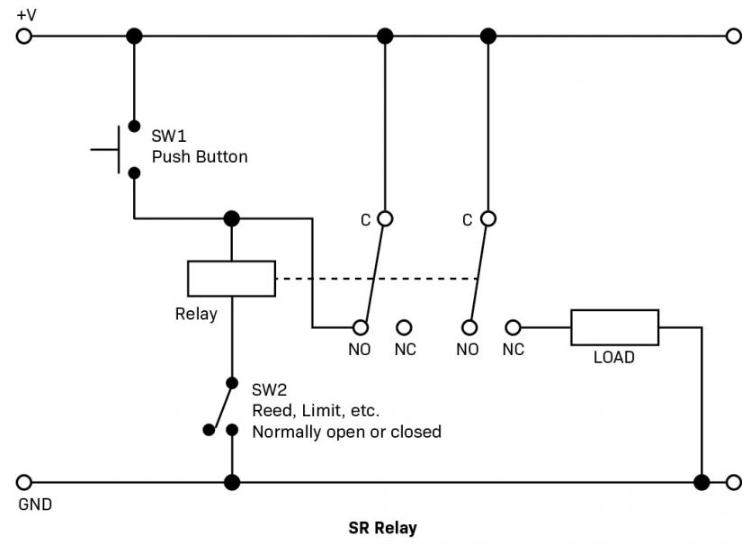

1. Relay latch

When SW1 is pressed, the current flows through relay coil, closing the contacts. This switches on the load. The circuit remains latched in this state until power is disconnected OR if SW2 is closed.

NOTE: SW2 can be a reed, limit or float switch.

This basic circuit can be used to manually turn on a water tank fill pump, then using a float switch to turn it off when full.

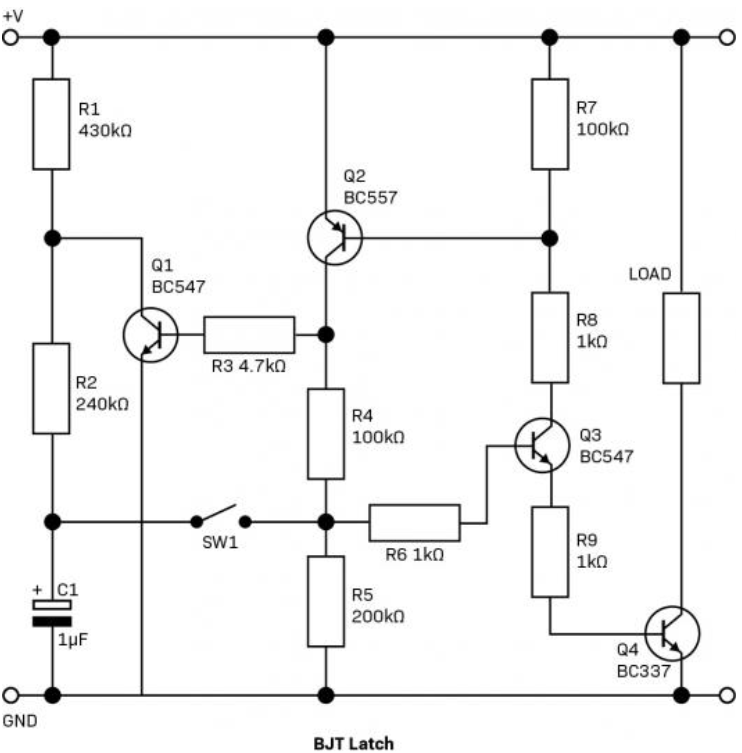

2. BJT Latch

This is a one-button based latching circuit.

The schematic might seem overwhelming but I will explain it:

- Initially ALL transistors are off and C1 is charging via R1 and R2 (note their large resistances)

- Once switch is pressed, Q3 toggles on. With a small current flowing through R4 and R5 (but current takes path of least resistance which is R6)

- Q3 toggles Q2. Q2 keeps Q3 on, latching the circuit

- Q2 toggles Q1

- This drains C1 through Q1 to ground BUT this occurs slowly due to R2’s high resistance

- Thus, after button press, circuit is latched and C1 gradually falls to 0V potential

- Once button is pressed, C1 sinks current, diverting it from Q3

- Q3 toggles which toggles Q2 which toggles Q1. C1 begins charging again

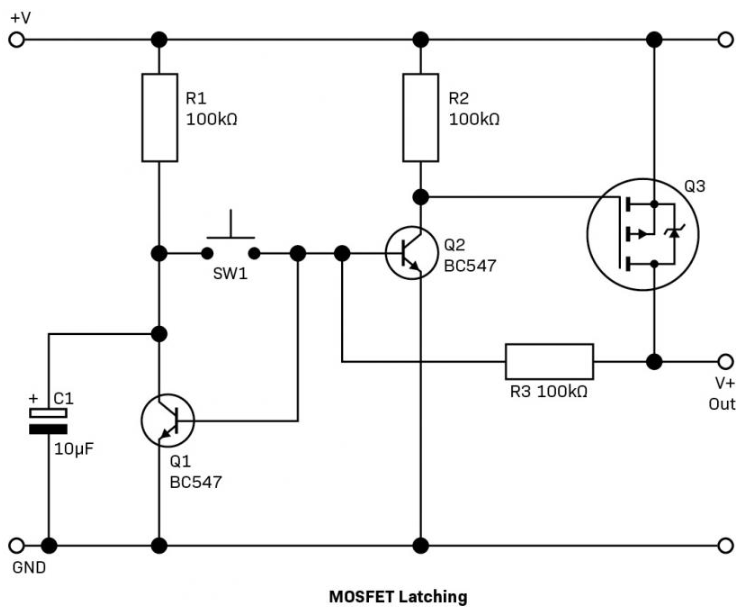

3. MOSFET latch

This circuit similar to the BJT version above. However, it’s aimed more at controlling power to a whole circuit rather than a specific load or section of a circuit. FET’s are used since their more efficient

Initially, SW1 is open. C1 charges via R1. Q3, a P-channel FET is also off. Recall, that N-channel FET’s conduct on a negative V_GS as opposed to a N-channel FET that conducts on a positive V_GS.

Pressing SW1 causes Q2 to conduct. This allows Q3 to conduct as it’s Gate is being shorted.

R3 connects to the base of Q2 and Q1. This is a form of feedback.

C1 slowly discharges via Q1. keeping Q3 high after SW1 is open.

Next time the button is pressed, the base of Q2 is grounded because there is no longer a voltage here, and it turns off, allowing the gate of Q3 to be pulled high by R2 and turning off the circuit. We are now back to where we started

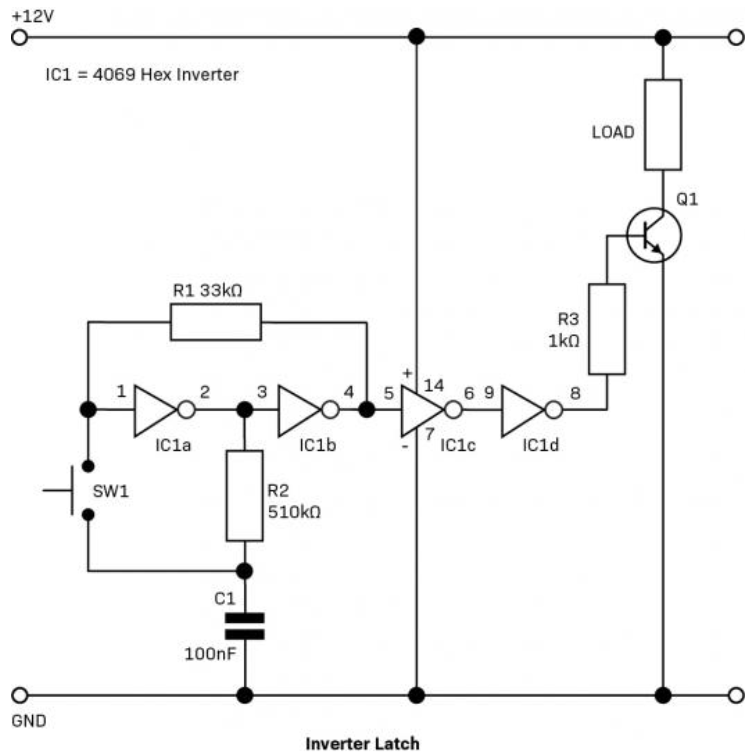

4. Inverter latch

This circuit has a unique feature. It is self-debouncing.

- On power-up, the first inverter has a low input, and therefore a high output.

- The high output flows to the input of the second inverter, which is then held with its output low because the input is high.

- The capacitor C1 charges through R2.

- When the pushbutton is pressed, the capacitor voltage is transferred to the input of the first inverter, showing as a high on its input.

- Now, its output switches low.

- That low is presented to the input of the second inverter, the output of which now goes high and is connected by the feedback resistor R1 to the input of the first inverter, holding this in the high state after the pushbutton is released.

- At this point, the capacitor is discharged and stays that way because it is connected to the low section between the two inverters.

The next time the button is pushed, the capacitor presents a lower impedance to the current through R1 than the input of the first inverter, so it charges, dropping the voltage at first.

Before it can charge up again, the output of the first inverter goes high in response to the low input. Now, the capacitor can charge through R2, but slowly because of its value.

The input of the second inverter is now high, so its output goes low, removing the high provided by R1.

As the button is released, this state is maintained and the capacitor charges through R2 ready for next time.

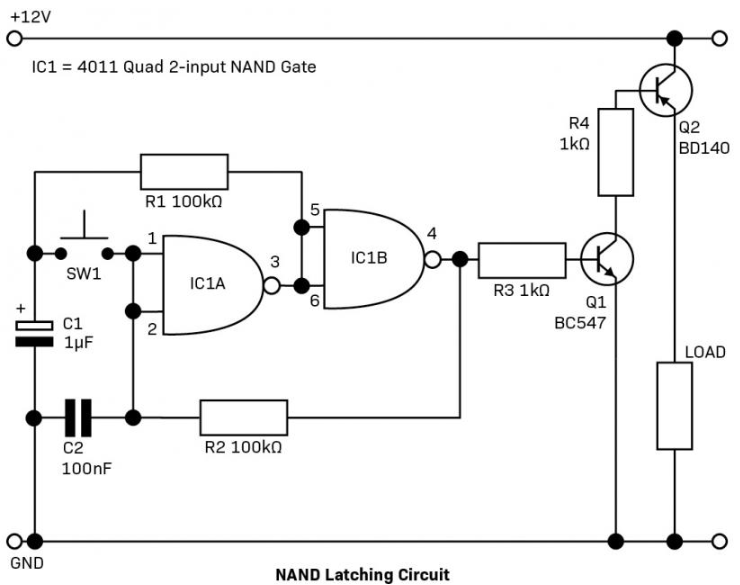

5. NAND latch

This circuit is almost identical to the previous circuit.

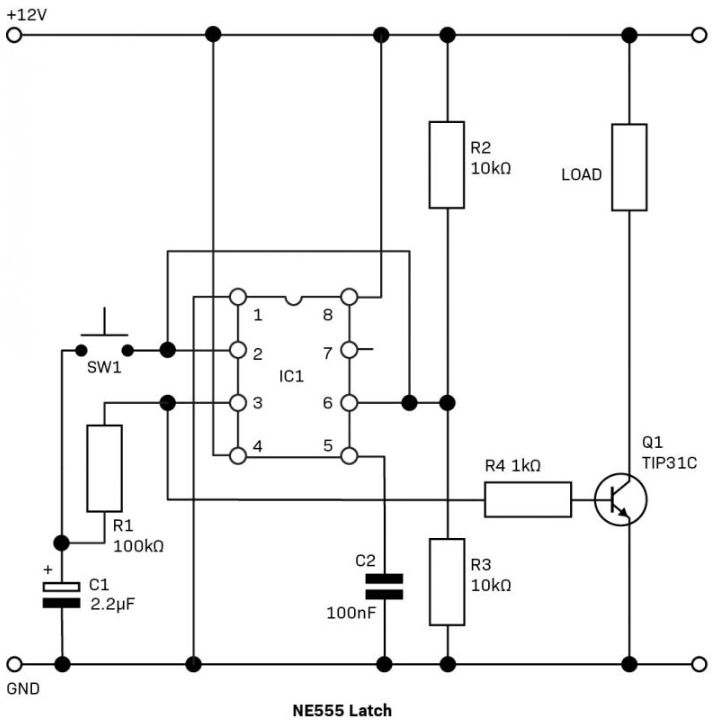

6. NE555 Latch

Upon power-up, the output (pin 3) is low. SW1 is connected to a voltage divider that halves the supply voltage. When it is pressed, Pin 2 drops below 1/3VCC, toggling the internal flip-flop. This sets pin 3 high, causing Q1 to conduct. Simultaneously C1 begins to charge via R1.

When SW1 is pressed again, pin 3 goes low. Pin 3 sinks the voltage at C1.

Thanks to the NE555’s 200mA source/sink current, the loads that it can drive can be substantial such as a 12V globe.

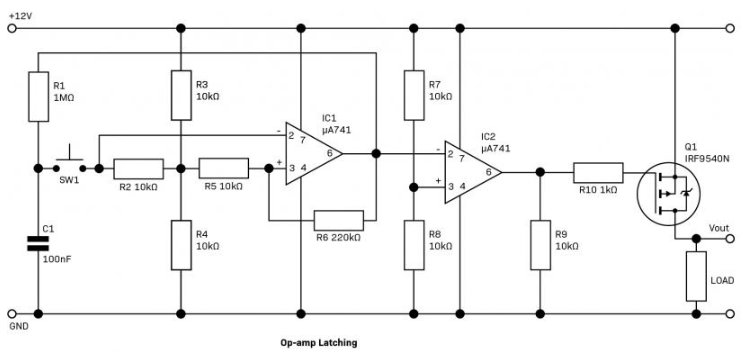

7. Opamp latch

Initially the output is low. The non-inverting input of IC1 is held at 1/2 the supply voltage via the voltage divider. R6 provides positive feedback. IC1 is configured as a comparator.

When SW1 is pressed, the inverting input is shorted via C1. IC1 goes high, with the output swinging towards VCC. At this stage, C1 begins charging through R1.

C1 will not charge significantly because of the two 10kΩ resistors R2 and R4 providing a ground path. The circuit remains in this state until the button is released.

The output state stays locked, because there is positive feedback to the non-inverting input via R6.

The capacitor, however, is now free to charge to the output voltage.

Next time the button is pressed, this voltage is presented to the inverting input, and is well above the reference voltage at the non-inverting input. Thus, the output goes low. Now, the circuit is back where it started.

IC2 is a buffer. It’s purpose is to prevent Q1 from loading IC1

In Closing

The circuits presented in this page used a tactile pushbutton as an input. However, any input can be used.

If you do decide to use a pushbutton, placing a 1nf – 100nF cap in parallel will prevent debouncing.

The output stage can be anything you desire. FETs, transistors, relays etc.

Feel free to adjust the circuit parameters. The best way to learn is through experimenting.